探秘X86架构CPU流水线

英文原文:A Journey Through the CPU Pipeline

作为程序员,CPU 在我们的工作中扮演了核心角色,因此了解处理器内部的工作方式对程序员来说不无裨益。

CPU 是如何工作的呢?一条指令执行需要多长时间?当我们讨论某个新款处理器拥有 12 级流水线还是 18 级流水线,甚至是更深的 31 级流水线时,这到些都意味着什么呢?

应用程序通常会将 CPU 看作是黑盒子。程序中的指令按照顺序依次进入 CPU,执行完之后再按顺序依次从 CPU 中出来,而内部到底发生了什么,我们通常并不了解。

对我们程序员来说,尤其是对做程序性能调优工作的程序员来说,学习 CPU 内部的细节非常必要。否则,如果你不知道 CPU 的内部结构,那如何才能针对 CPU 做性能优化?

本文所关注的就是专门针对 X86 处理器流水线的工作原理。

你需要掌握的预备知识

首先,阅读本文你需要了解编程,最好了解一点汇编语言。如果你还不知道指令指针(instruction pointer)是什么,那么本文对你来说可能有些难。你需要知道什么是寄存器,指令和缓存,如果不明白它们是什么,你需要尽快查找资料了解一下。

第二,CPU 的工作原理是一个非常庞大和复杂的话题,本文仅仅是匆匆一瞥,很难以用一篇文章详尽叙述。如果我有什么疏漏,请通过评论告诉我。

第三,我仅仅关注英特尔处理器及其 X86 架构。当然除了 X86,还有很多其他架构的处理器。虽然 AMD 公司引入了很多新特性到 X86 架构,但是 X86 架构是 Intel 公司发明,并且创造了 X86 指令集,其中绝大多数特性是由 Intel 引入的。所以为了保持叙述的简单和一致性,我仅关注 Intel 的处理器。

最后,当你读到这篇文章时,它已经是“过时”的了。更新款的处理器已经设计出来,其中一些会在未来几个月之内发布。我很高兴技术能如此快速的发展,我希望有一天所有这些技术都会过时,创造出拥有更惊人计算能力的 CPU.

处理器流水线基础

从一个非常广的角度来说,X86 处理器架构在近 35 年来并没有变化太多。虽然 X86 架构被附加了很多新功能,但是最初的设计(包括几乎所有最初的指令集)仍然基本上是完整保留的,即使在最新的处理器上仍然被支持。

最初的 8086 处理器支持 14 个寄存器,这些寄存器在如今最新的处理器中仍然存在。这 14 个寄存器中,有 4 个是通用寄存器:AX,BX,CX 和 DX;有 4 个是段寄存器,段寄存器用来辅助指针的实现:代码段(CS),数据段(DS),扩展段(ES)和堆栈段(SS);有 4 个是索引寄存器,用来指向内存地址:源引用(SI),目的引用(DI),基指针(BP),栈指针(SP);有 1 个寄存器包含状态位;最后是最重要的寄存器:指令指针(IP)。

指令指针寄存器是一个拥有特殊功能的指针。指令指针的功能是指向将要运行的下一条指令。

所有的 X86 处理器都按照相同的模式运行。首先,根据指令指针指向的地址取得下一条即将运行的指令并解析该指令(译码)。在译码完成后,会有一个指令的执行阶段。有些指令用来从内存读取数据或者向内存写数据,有些指令用来执行计算或者比较等工作。当指令执行完成后,这条指令会通过退出(retire)阶段并将指令指针修改为下一条指令。

译码,执行和退出三级流水线组成了 X86 处理器指令执行的基本模式。从最初的 8086 处理器到最新的酷睿 i7 处理器都基本遵循了这样的过程。虽然更新的处理器增加了更多的流水级,但基本的模式没有改变。

35 年来发生了什么改变

相较于现今的标准,最初的处理器设计显得太过简单。最初的 8086 处理器的执行过程可以简述为从当前指令指针取得指令,通过译码,执行最后退出,然后继续从指令指针指向的下一条指令处取得指令。

新的处理器增加了新的功能,有些增加了新的指令,有些增加了新的寄存器。我将主要关注和本文主题有关系的改变,这些改变影响了 CPU 指令执行的流程。其他的一些变化比如虚拟内存或者并行处理虽然都很有意义而且有趣,但是并不在本文主题的范围内。

指令缓存在 1982 年被加入到处理器中。通过指令缓存,处理器可以一次性从内存读取更多指令并放在指令缓存中,而不用每条指令都从内存中取。指令缓存仅有几个字节大小,只能容纳数条指令,但是因为消除了之后每次取指往返内存和处理器的时间,极大的提高的效率

1985 年的 386 处理器引入了数据缓存,而且扩展了指令缓存的设计。数据访存请求通过一次性读取更多的数据放在数据缓存中,从而提升了性能。而且,数据缓存和指令缓存都从几个字节扩大到几千字节。

19巴久年推出的 i486 处理器引入了五级流水线。这时,在 CPU 中不再仅运行一条指令,每一级流水线在同一时刻都运行着不同的指令。这个设计使得 I486 比同频率的 386 处理器性能提升了不止一倍。五级流水线中的取指阶段将指令从指令缓存中取出(i486 中的指令缓存为 8KB);第二级为译码阶段,将取出的指令翻译为具体的功能操作;第三级为转址阶段,用来将内存地址和偏移进行转换;第四级为执行阶段,指令在该阶段真正执行运算;第五级为退出阶段,运算的结果被写回寄存器或者内存。由于处理器同时运行了多条指令,大大提升了程序运行的性能。

1993 年 Intel 推出了奔腾(Pentium)处理器。由于诉讼问题,Intel 无法继续沿用原来的数字编号。因此,用奔腾替代了 586 作为新款处理器的代号。奔腾处理器相对 i486 处理器对流水线做出了更多修改。奔腾处理器架构增加了第二条独立的超标量流水线。主流水线工作方式类似于 i486,第二条流水线则并行的运行一些较简单的指令,比如说定点算术,而且该流水线能更快的进行该运算。

1995 年 Intel 推出了奔腾 Pro (Pentium Pro)处理器。和之前的处理器相比,奔腾 Pro 采用了完全不同的设计。该处理器采用了诸多新特性以提高性能,包括乱序(Out-of-Order, OOO)执行的部件以及猜测执行。流水线扩展到了 12 级,而且引入了“超标量流水线”的概念,使得许多指令可以被同时处理。我们稍后将详尽的介绍乱序执行的部件。

在 1995-2002 年之间,乱序执行部件经过了数次重大改进。处理器中加入了更多的寄存器;单指令多数据(Single Instruction Multiple Data, or SIMD)的引入使得一条指令可以进行多组数据运算;现有的缓存变得更大而且引入了新的缓存;有些流水级被拆分成更多流水级,有些流水级被合并,使得更加适合实际的应用。这些改变对整体性能的提升有重要作用,但它们都没有从根本影响数据在处理器中的流动方式。

2002 年发布的奔腾 4 处理器引入了超线程技术。乱序执行部件的设计使得指令被执行的速度比处理器能够提供指令的速度更快。因此对于大部分应用,CPU 的乱序执行部件在大部分时间处于空闲状态,甚至在高负载的情况下也不能充分利用。为了让指令流能充分的流入乱序执行部件,Intel 加入了第二套前端部件(译注:在处理器结构中,前端是指取指,译码,寄存器重命名等模块,经过前端部件的处理后,指令等待发射进入乱序执行部件)。虽然实际上只有一个乱序执行部件,但对于操作系统来说,它能看到两个处理器。前端部件包含两组同样功能的 X86 寄存器,两个指令译码器根据两个指令指针指向的地址分别处理。所有的指令被一个共享的乱序执行部件执行,但对应用程序来说并不知情。当乱序执行部件执行完成,像之前一样退出流水线后,最终结果返回虚拟的两个处理器。

2006 年 Intel 发布了酷睿(Core)微架构。为了品牌效应,它被称做酷睿2(二总比一好)。令人惊讶的是,处理器频率不升反降,而且超线程也被去掉了。通过降低时钟频率,每一级流水线可以做更多工作。乱序执行部件也被扩展的更宽。各种不同的缓存和队列都相应做的更大。而且处理器被重新设计,以适应双核和四核的共享缓存结构。

2008 年,Intel 开始用酷睿 i3, i5, i7 的方式来命名新的处理器。新处理器重新引入了超线程。这三个系列的处理器主要区别在于内部缓存大小不同。

未来的处理器:Intel 的下一代微结构被称为 Haswell.Haswell 据称将于 2013 年发布。目前已知的文档说明它将拥有 14 级流水级的乱序执行部件,所以它仍然遵循从奔腾 Pro 以来的基本设计思路。

那么,流水线到底是什么?乱序执行部件是什么?他们如何提升了处理器的性能呢?

CPU 指令流水线

根据之前描述的基础,指令进入流水线,通过流水线处理,从流水线出来的过程,对于我们程序员来说,是比较直观的。

I486 拥有五级流水线。分别是:取指(Fetch),译码(D1, main decode),转址(D2, translate),执行(EX, execute),写回(WB)。某个指令可以在流水线的任何一级。

但是这样的流水线有一个明显的缺陷。对于下面的指令代码,它们的功能是将两个变量的内容进行交换。

XOR a, b

XOR b, a

XOR a, b

从 8086 直到 386 处理器都没有流水线。处理器一次只能执行一条指令。再这样的架构下,上面的代码执行并不会存在问题。

但是 i486 处理器是首个拥有流水线的 x86 处理器,它执行上面的代码会发生什么呢?当你一下去观察很多指令在流水线中运行,你会觉得混乱,所以你需要回头参考上面的图。

第一步是第一条指令进入取指阶段;然后在第二步第一条指令进入译码阶段,同时第二条指令进入取指阶段;第三步第一条指令进入转址阶段,第二条指令进入译码阶段,第三条指令进入取指阶段。但是在第四步会出现问题,第一条指令会进入执行阶段,而其他指令却不能继续向前移动。第二条 xor 指令需要第一条 xor 指令计算的结果a,但是直到第一条指令执行完成才会写回。所以流水线的其他指令就会在当前流水级等待直到第一条指令的执行和写回阶段完成。第二条指令会等待第一条指令完成才能进入流水线下一级,同样第三条指令也要等待第二条指令完成。

这个现象被称为流水线阻塞或者流水线气泡。

另外一个关于流水线的问题是有些指令执行速度快,有些指令执行速度慢。这个问题在奔腾处理器的双流水线架构下显得更加明显。

奔腾 Pro 拥有 12 级流水线。当这个数字被首次宣布后,所有的程序员都倒抽了一口气,因为他们知道超标量流水线是如何工作的。如果 Intel 仍然按照以前的思路设计超标量流水线的话,流水线的阻塞和执行速度慢的指令会严重影响执行速度。但同时,Intel 宣布了完全不同的流水线设计,叫做乱序执行部件(Out-of-Order core)。单从叙述上很难理解这些改变带来的好处,但 Intel 确信这些改进是令人激动的。

让我们来更深入的看看这个乱序执行的部件吧!

乱序执行流水线

在描述乱序执行流水线时,往往是一图胜千言。所以我们主要以图例进行介绍。

CPU 流水线图例

I486 处理器拥有 5 级流水线。这种设计在现实世界中的其他处理器中很常见,而且效率不错。

而奔腾处理器的流水线比 i486 更好。两条流水线可以并行运行,而且每条流水线可以同时有多条指令在不同流水级执行。它几乎可以同时执行比 i486 多一倍的指令。

能够快速完成的指令需要等待前面执行慢的指令即使在并行流水线中也仍然是一个问题。流水线仍然是线性的,导致处理器面临性能瓶颈难以逾越。

乱序执行部件和之前处理器设计中的线性通路有很大不同,它增加了一些复杂度,引入了非线性的通路。

标签:

- 折叠屏手机成为各大厂商发力的对象 2022年出货量有望达1750万台

- 酷比魔方新品iWorkGT发布 配11英寸全贴合屏幕 功能接口齐全

- Xbox One主机确认停产 官方表示将在2022年重启PS4的生产线

- 外挂开发商通知将停止对《战地2042》外挂更新 不值得继续维护

- 三星全新显示技术QD-OLED将是香饽饽 带来的画质提升让人充满期待

- 曝天玑9000旗舰手机春节后登场 包含一些真正的顶配旗舰

- 微信红包变样了! “摇动”手机即可领取SS22异形红包封面

- 2021年中国互联网广告收入榜 阿里巴巴位列榜单首位

- 锂电池新型电解质面世 可以有效抑制锂枝晶的出现

- NVIDIA获评美国最佳工作场所 NVIDIA获得榜单第一的宝座

- 东北女子网购金鱼收到冻成冰坨 网友热议网购生物不合常理吧?

- 小鹏汽车转让嘉兴智鹏全部股权 新增股东嘉兴鹏行将100%持股

- 《长津湖之水门桥》定档大年初一 今年春节档的动画电影多达5部

- R星母公司T2财报暗示 计划在2024年3月前发布《GTA6》

- 手工耿发明第二代卫生纸加热器 网友调侃直接发明加热马桶多好

- 通用汽车高管:公司待上线CarBravo网站将便于用户购买二手车

- 挑战锂离子电池的锂金属电池来了 多家龙头公司的同时参股

- 女子网购iPhone遭快递员强拆验货 网友表示快递员估计以前吃过亏

- 北京冬奥会火炬将在三个赛区传递 “飞扬”的材料采用了“碳纤维”

- 保时捷2021年销量创下全新纪录 Taycan等电动车款式增势喜人

- IDC副总裁: 今年PC市场或迎来进一步发展 但同时存在诸多挑战

- Intel Arc显卡冒出来20个版本 这些设备ID目前都是禁用状态

- 苹果认证配件商推出145元抛光布平替款 支持多次水洗

- 脑瘫女孩求输入法“破解” 搜狗输入法团队接手这个输入法

- 时隔5年再次拥抱AMD显卡 发布了自己的RX 6600 XT

- 母亲被指“老赖” 女UP主致歉 决定退出B站评选的百大UP主

- Intel未发布下代至强被开盖 每颗计算芯片上有16个核心

- 全球首个家用万兆Modem测试成功 上传速度超过了4Gbps

- 舅舅给外甥包50亿红包只值5毛钱 网友调侃这版好几年前已经作废了

- 曝英伟达将加强首批RTX3050货源铺货 到仓时间预计为春节后

- AMD的锐龙7 5800X3D处理器曝产能紧张 增加了额外64MB缓存

- 索尼FX6电影摄影机即将发布新固件 虚化调整模式等新功能将至

- 撼讯RX6500XTmini-ITX显卡或下周上市 GPU实测频率尚待公布

- 抖音又有大动作!封禁52万个涉嫌诈骗账号

- PowerToys工具集发布v0.53.3正式版 软件运行速度将获提升

- 微软推出Win11最新Dev预览版 将重置天气小部件优化体验

- 微软Xbox负责人:比起XGP 游戏玩家还是更注重传统销售方式

- MIUI13稳定版已推送至小米10S手机 基础体验将得到更多优化

- 戴尔高级副总裁谈XPS13Plus新品:全为创作者开发升级众多

- MIXFOLD2折叠机曝光 外屏更换为玻璃材质 ID设计发生变化

- 索尼原计划停产的PS4确认继续生产:旨在缓解PS5无货状况

- Canalys最新数据表明:个人电脑全年出货量已同比上涨15%

- 英飞凌官宣最新一代CAPSENSE技术 并可提供多个先进解决方案

- Redmi官方发布蜘蛛侠联动海报 以其迅捷身手宣传120W秒充

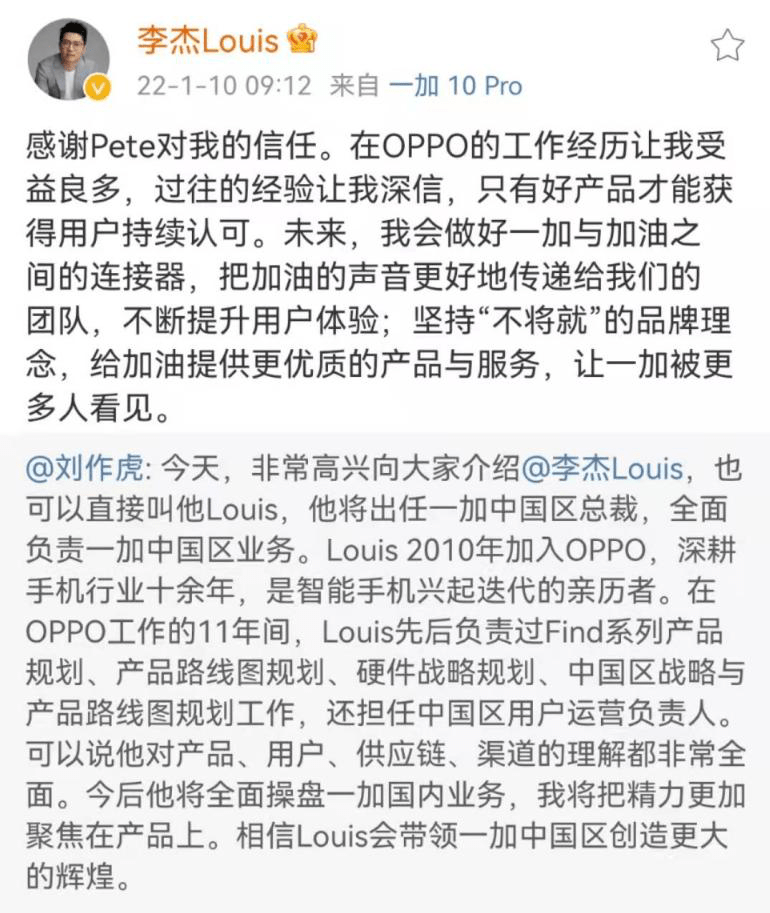

- OPPO首席产品官刘作虎点评新机一加10Pro:表现全方位的稳

- 百度起诉我爱网获赔200万 帮助用户制造虚假点击数据

- 国产虚幻4大作上架国行PS商店 将收录目前所有游戏更新的扩展内容

- 雷军回忆小米12“黄金手感”诞生过程 澄清很多消费者的一个误区

- 搜狐CEO张朝阳登上长白山开启超长直播:三天三夜出镜不间断

- 统信操作系统V20龙芯版正式发布 拥有人性化的桌面环境

- 传iPhone14Pro将升级4800万像素广角镜头 影像力进一步提升

- 罗技发布LitraGlow照明设备 可为流媒体视频录制提供更好的打光

- 索泰RTX 3080 12G6X PGF OC显卡图赏 支持ARGB灯效分区控制

- 四盘位NAS极空间新Z4图赏 采用Intel J4125处理器

- Microchip发布全新编程开发工具MPLAB ICE4 速度已达到极致

- Redmi Note 11S宣布 采用类似Redmi Note 11的矩阵相机设计

- 高端新能源SUV销量榜 宝马iX3是BBA电动车中销量最高车型

- iPhone14手机定价曝光 全部型号一致比苹果13系列高出一百美元

- 一加蓝帅称OPPO/一加社区可能联合举办活动 但暂未有合并计划

- vivoNEX5核心配置遭曝光 或惊喜配置7英寸大屏幕以及长效续航

- Redmi《蜘蛛侠3》联动引热议 网友开喷发了几张海报就算联名了

- NVIDIA为7年前Shield TV升级安卓11系统 带来一些功能升级

- OPPO进入21年度美国专利授权榜Top50 总719项授权同增三成

- 徐起盛赞真我GT2Pro超大内存版:为年轻用户带来更大存储空间

- Firefox96正式版来了 可兼容Win/Linux/macOS 运行速度起飞

- 老赖拖欠20多万不还 B站CEO陈睿“力捧”其女儿至百大UP主

- 湖南小伙隐居深山4年造出一个桃花谷 网友评论实实在在的扎根农村

- OPPO K9x机型也推出限时立减 可选两款配色 大容量电池续航长

- 宁德时代申请无负极金属电池专利 能量密度为160Wh/kg

- 2GB内存的树莓派4就能跑Ubuntu 22.04 背后优化的秘密是Zswap

- 大屏版Android 12L放出Beta2 系统特性和API已经定型

- 传长城和路虎成立合资公司 长城汽车正面否认该传闻

- RTX 3050供货将大大增加 预计渠道方面大量开卖要等到春节后

- 报道称新款27英寸iMacPro将在三月推出 并采用M1Max处理器

- 博物馆将名画夜巡数字化并发布超高清照片 细节纹路分毫毕现

- 爆料称iPhone 14将采用双开孔设计 是感叹号形状的开孔

- 荣耀总裁科普Magic V折叠屏 向设计能力和制造工艺发起挑战

- realmeBook增强版笔记本推出年货好价 极致轻薄机身更易携带

- 三星Galaxy Tab S8高端平板现身韩国认证网站 屏幕均采用四等边框

- 一加李杰解读新旗舰外观:全新材质打破常规 细节用心质感更出众

- 红魔7跑分出炉 将搭载主动散热级骁龙8 Gen1

- 魅蓝回归第二款新机入网 3C认证信息显示该机将支持10W充电

- 小米10S推送MIUI 13稳定版 搭载号称业内最好的双立体声扬声器

- 三星手机与京东战略合作 全方位提升三星在国内手机市场的销量

- 集邦咨询:预测今年智能机相机模组出货量将持续增长至49.2亿颗

- 飞傲正式推出FHE圈铁耳机 新品支持换线使用 高频延展表现佳

- 消息称Redmi K50系列全员打孔屏 将会推出冲击高端价位的机型

- 京东上架荣耀Magic V茅台套装版 将于1月18号首销

- Intel锐炫显卡完成重要优化 一经发布即可用上强劲Linux驱动

- 曝Redmi K50电竞版保留侧面指纹 将指纹模块嵌入功能键中

- 曝iPhone 14 Pro采用双挖孔屏幕 圆孔存放Face ID的点阵模块

- 曝谷歌Pixel Fold神似OPPO Find N 谷歌Pixel Fold代号为“Pipit”

- 丰田全新坦途Capstone皮卡来袭 外观用上整车镀铬装饰尽显豪华

- 一加10 Pro正式开售 采用三星6.7英寸AMOLED顶级屏幕

- 曝vivo NEX新品用7英寸超大屏 后置主摄为5000万像素

- Intel奔腾G7400处理器上架销售 多款新酷睿i5处理器也已开卖

- 中国电信推出天翼空中上网产品 支持在线音视频等办公及娱乐服务

- 英特尔赛扬G6900入门级处理器水准分析:单核胜过i9-10900K

- 小姐姐实测小米12 Pro充电 速度位列第一梯队

- realme GT2 Pro首个系统更新 新增视频模式Al视频增强功能

新闻排行

- 酷派手机:将追究快手主播“驴嫂平荣”直播间售卖山寨机的责任

- 荣耀平板V7 Pro今日开售 采用高导热铝合金中框

- Redmi 10在马来西亚举行发布 采用居中挖孔屏方案

- iQOO 8 Pro作为iQOO最强大的旗舰 首发多项核心技术

- 小米平板5 Pro 6GB+128GB版本现货发售 支持67W闪充

- 飞行员iPhone X从3千米高空跌落 因戴配套保护壳幸运保持完好

- 一加Nord 2 5G手机将于近日在海外发布 搭载天玑1200-AI处理器

-

小米手机屏下摄像头专利上月获欧洲专利局和美国专利商标局的专利授权

小米手机屏下摄像头专利上月获欧洲专利局和美国专利商标局的专利授权 -

OPPO将为旗舰机带来最大7GB内存扩展 为低内存手机带来更好的体验

OPPO将为旗舰机带来最大7GB内存扩展 为低内存手机带来更好的体验 -

荣耀选择单电芯双回路技术 提高快充速度是目前解决用户“电量焦虑”问题的方法之一

荣耀选择单电芯双回路技术 提高快充速度是目前解决用户“电量焦虑”问题的方法之一

精彩推荐

超前放送

- 京东家电年货节盛大开启 多家线...

- 红米K50电竞版工程机曝光 爆料...

- 红魔7新机入网 后置摄像模组为...

- 最新版高德地图推出超好用功能 ...

- vivo最新上架Y10与t1新机 定价1...

- 育碧新版工人物语预告视频来了 ...

- 华硕破晓Pro15笔记本:搭载全新...

- 摩托罗拉edgeX30喜获2021最具影...

- 小米音频输出模式调整相关专利获...

- INNOCN海外发布全新4K液晶显示器...

- AppleProCam8K视频相机新图曝光...

- IP衍生手游《阿凡达:清算》首曝...

- 索尼将停售PlayStationNow储值卡...

- Noble限量耳机VIKING正式发布 ...

- 小米CEO雷军:又有一款产品全量...

- 散热器厂商Noctua更新产品路线图...

- 传TOP5大厂旗舰新品将用上12/13...

- 爆料称新款锐龙4000系列桌面处理...

- 不带身份证也能坐火车了!12306...

- OPPO新品现身Geekbench 测试者I...

- 福特汽车官宣:去年已完成覆盖范...

- 方形版小米智能手环专利获得授权...

- 七彩虹高端硬件显卡新品上架京东...

- 比亚迪全新测试车谍照曝光 外壳...

- 2022年油价第一涨!加满一箱92号...

- 小红书申请老红书商标获批 网友...

- 4月北京骑共享单车需实名认证 ...

- 福特超级跑车现身拍卖网 搭载一...

- 酷派COOL 20 Pro敦煌鎏金版开...

- 小米12系列即将亮相海外 Pro版...

- Redmi K50电竞版工程机参数曝光...

- 小米12 Pro新年礼盒版明天首销...

- Redmi Note 11S外形曝光 后置...

- 英特尔Arc锐炫显卡忽现20个新版...

- 黑鲨游戏手机新旗舰曝光 该机将...

- 调研机构:21年第四季度HDD出货...

- 萤宝虎年限定礼盒来了 拥有十八...

- 英特尔待发布处理器已被拆解开盖...

- 爆料称多款RedmiK50系列机型将采...

- 小米与多家高校共建工作室陆续启...

- 三星全新笔电设计专利获批:键盘...

- OPPO FindN手机再次开售 定价...

- 乂度最新解码耳放Link2Bal发布 ...

- SurfaceLaptopSE维修视频上线 ...

- 设计师详解小米12系列后置摄像模...

- 等老了改名吗?小红书成功注册老...

- OPPO Find N今日10点再次开售...

- 电竞手机红魔7入网 该机整体延...

- 红魔7入网照片公布 后壳采用大...

- K50 Pro系列曝光 Redmi K50搭...

- 曝天玑9000机型3月上市 安兔兔...

- 12306手机App电子临时乘车身份证...

- 全新丰田Noah/Voxy官图发布 新...

- 丰田GR YARiS GRMN发布 拥有...

- 大众集团发布销量报告 大众中国...

- 五菱E230专利图曝光 将提供更小...

- 宏光MINIEV 2021年销量42.6万台...

- 北京越野BJ40环塔冠军版交付 采...

- 日产全新跑车Z开售 采用标志性...

- Xbox产品营销高级总监:为专注于...

- 英特尔i7-12700盒装处理器来了 ...

- XboxSeriesX|S在英国达成百万台...

- 荣耀公布使用可穿戴设备排队叫号...

- 英伟达高管:公司显卡供应短缺状...

- 原神安卓版更新上线 对骁龙8/天...

- 乘联会现发布12月销量排名快报:...

- 雷蛇2022款灵刃14笔记本:标配R9...

- 索尼发布无线颈挂式扬声器新品 ...

- 昉星光VisionFive单板计算机已完...

- 宁德时代无负极金属电池专利曝光...

- 索尼电影公开神秘海域宣传海报 ...

- 体验玩法大更新 游戏宝可梦传说...

- 徕卡M11相机上架天猫并公开售价...

- 消息称小米正积极开发12款新机:...

- 英伟达SHIELD机顶盒更新9.0系统...

- 曝三星GalaxyTabS8系列有望即将...

- 传天玑8000新机将配置6.6英寸120...

- BlueTiger发布Solare太阳能耳机...

- 酷派COOL20Pro敦煌鎏金版正式发...

- 全球汽车销冠出炉 大众高端品牌...

- 轩辕剑柒上架索尼PS国行版商店 ...

- 雅迪亮相米兰国际摩托车展 采用...

- 奇瑞瑞虎8 PLUS鲲鹏e+预售价公...

- 90后艾玛沃特森晒新写真造型 全...

- SATA SSD硬盘爆出安全漏洞 美...

- 索尼发《神秘海域》中文预告 计...

- 路虎混动新车就出故障 4S店回复...

- 比亚迪中标智利锂矿开采 每份合...

- 蜂鸟Logo被“元宇宙项目”侵权使...

- NASA发布新一代太空望远镜主镜片...

- 映泰上架B660GTN ITX主板 将使...

- 《尼罗河上的惨案》新预告 故事...

- 近百只鸵鸟在广西街头狂奔 出现...

- 2022款ROG幻13晒出官方图赏 国...

- 年度最佳游戏终于登陆PC 该游戏...

- iPhone 14 Pro系列展望: 将...

- 《007:无暇赴死》1月15日登陆B...

- QQ音乐推出超级会员 专享免费线...

- 凤凰Phonenix-6静电圈铁耳机正式...

- 火狐官方回应新版浏览器无法访问...